In a recent post titled Simulating Knowm AHaH Memristor-Based Logic Using Qucs-S and Xyce, I presented circuit simulations that explored the dynamic behavior of the Knowm M-MSS (Mean Meta-stable Switch Memristor) model by creating basic logic circuits (i.e. 2-input AND, 2-input OR gate). We performed simulations using discrete memristor elements and sub-circuit models which implement neuromemristive synapses (i.e. AHaH kT-Synapses). In this post I will compare the simulation results from circuits designed using rectangle pulse generators with specific pulse timing to produce the truth table inputs to these logic circuits. As part of this tutorial we will selecting the Knowm JSpice simulator from the Qucs-S user interface and compare the simulation results to Xyce using the same M-MSS model and parameter values. In the example circuits presented here we will be using discrete memristor components to build the synapse circuits and we will be using the .model implementation found in the Knowm_Memristor_Technology library. The latest release candidate rc5 of the Knowm OSS EDA Stack also provides AHaH synapse nodes in the Knowm_AHaH_Nodes library implemented as sub-circuits to simplify building netlists for simulating the same basic logic circuits we’re going to design here. I’m going to leave this exercise for you to explore on your own but the equivalent circuits presented can be used as a guide. The Knowm_AHaH_Nodes library will be used in future tutorials which will demonstrate how to design and simulate neuromemristive circuits and machine learning algorithms in hardware.

These logic gate experiments will later be set up using actual discrete memristor devices using the Knowm Memristor Discovery board and associated extender modules. The following experiments are included in the example Qucs-S project AHaH_Logic_J_prj available in the examples_j_knowm_oss-eda-0.0.19s-rc5.dmg bundle.

Memristor Experiments Included in the Accompanying Examples

- ahah_mr_AND2_pl2

(2) Rectangular Pulse sources with positive pulse amplitude of 1V with transient analysis simulating an AHaH 1-2 synapse using discrete memristor elements configured to produce the logic states of a 2-input AND gate.

-

ahah_mr_OR2_pl2

(2) Rectangular Pulse sources with positive pulse amplitude of 1V with transient analysis simulating an AHaH 1-2i synapse using discrete memristor elements configured to produce the logic states of a 2-input OR gate.

NOTE: We will only be covering the AHaH 1-2 Synapse AND2 and the AHaH 1-2i (inverted) Synapse OR2 circuit in this tutorial.

Prerequisites

Update to the latest release candidate rc5 of the Knowm OSS EDA Stack. It is available for macOS 10.12 Sierra and Ubuntu 16.04 LTS (Xenial Xerus). This post covers installation and use on macOS and support for Xyce (Serial) and JSpice simulations only. JSpice is being delivered as an executable Java Archive .jar file. You will need to have Java installed on your computer before you can use the JSpice simulator. The versions of Qucs-S (0.0.19S) and Xyce 6.7 include libraries for amd64 architectures. Support for other architectures and operating systems are under development and will be released when available.

Please follow the detailed tutorial Comparing Simulation Results of the Knowm M-MSS Model in Xyce and JSpice Using Qucs-S to install and configure your OSS EDA Environment and copy the example JSpice projects to your $HOME/.qucs directory.

Overview

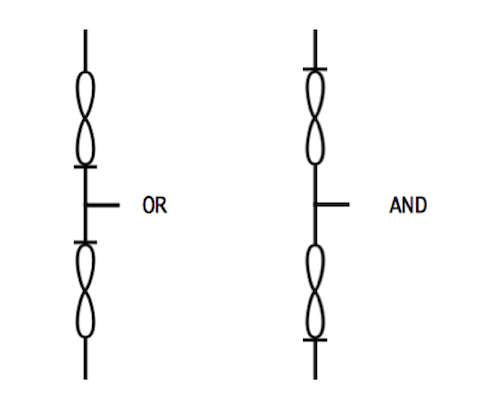

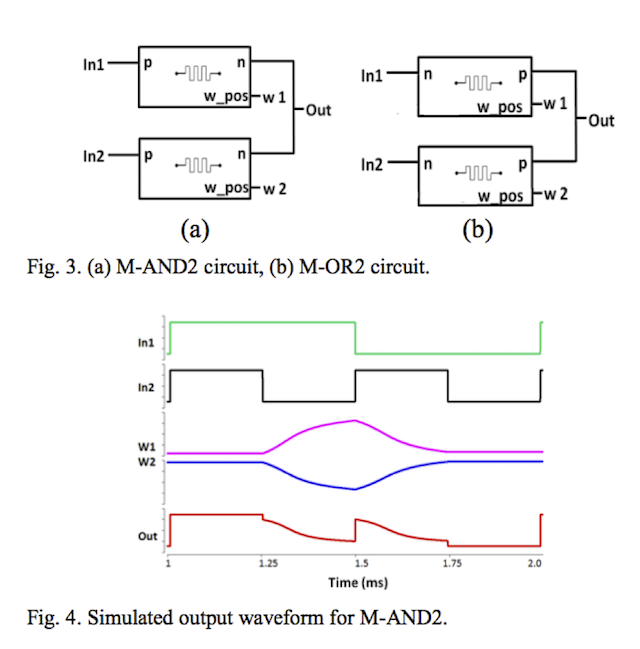

The following discussion of simulation of memristor logic circuits was developed based on the results of a paper presented by Frey, et. al. titled: “Investigating Power Characteristics of Memristor-based Logic Gates and Their Applications in a Security Primitive”. You may want to review this paper before or concurrently while working through this tutorial. The following configurations are the inspiration for the circuits we have configured here.

Open the AHaH Discrete Memristor AND2 Schematic diagram

- Double click the

AHaH_Logic_J_prjto automatically open the Content tab. -

Select the

ahah_mr_AND2_2pl.schfrom the Schematics list in the Contents tab of the Main Dock.

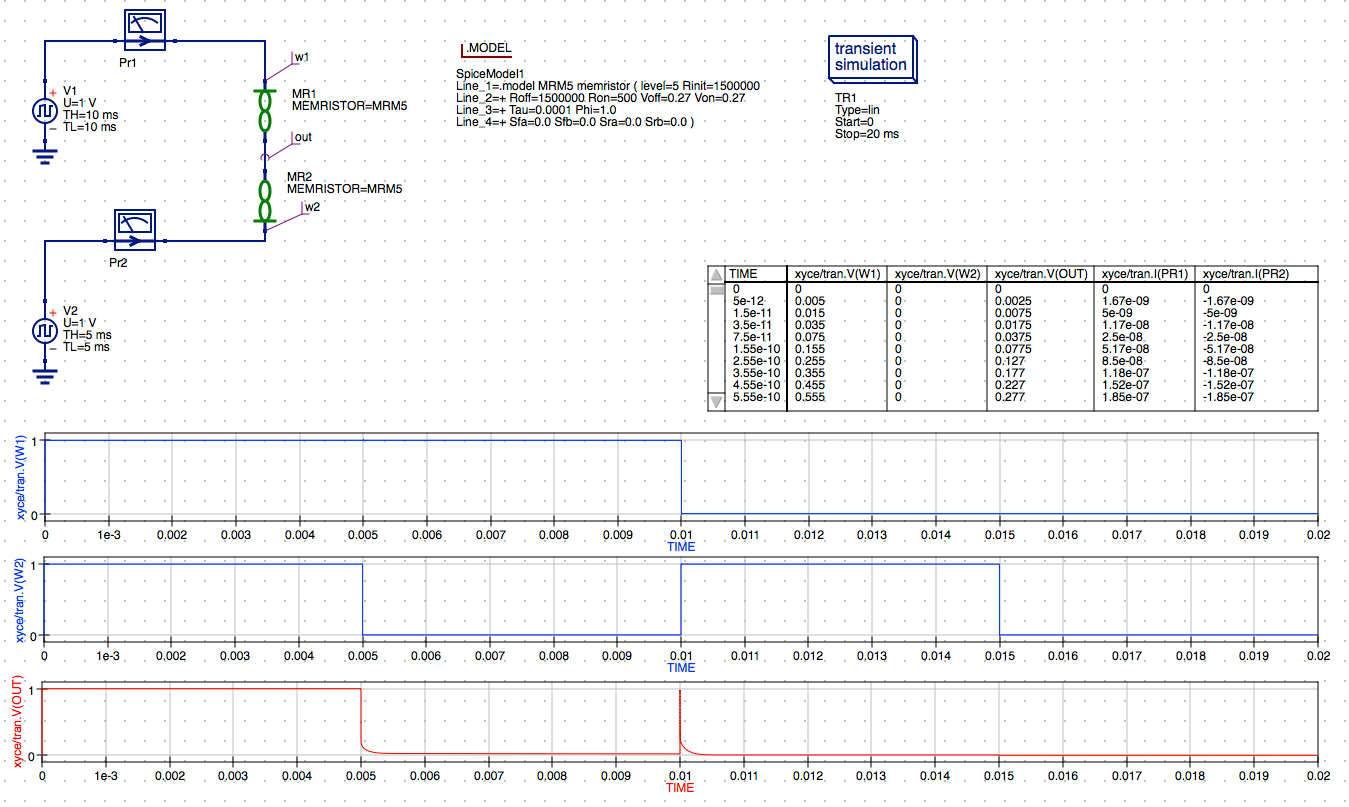

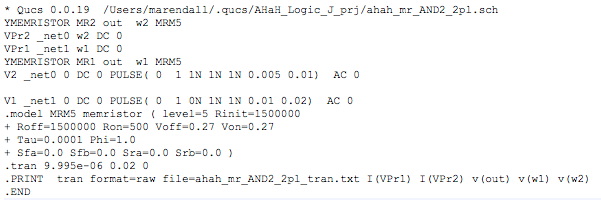

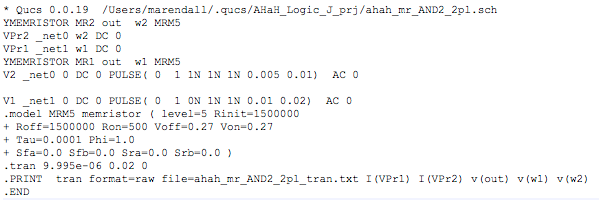

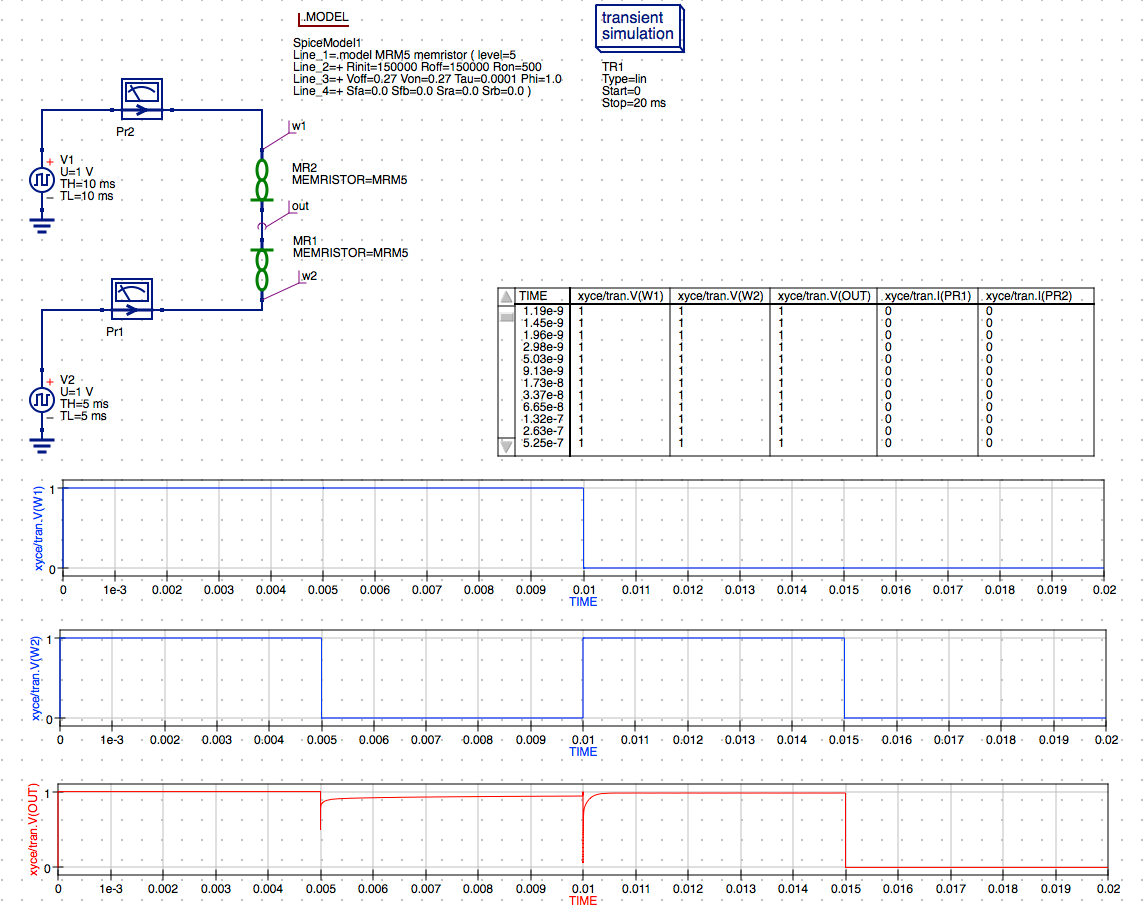

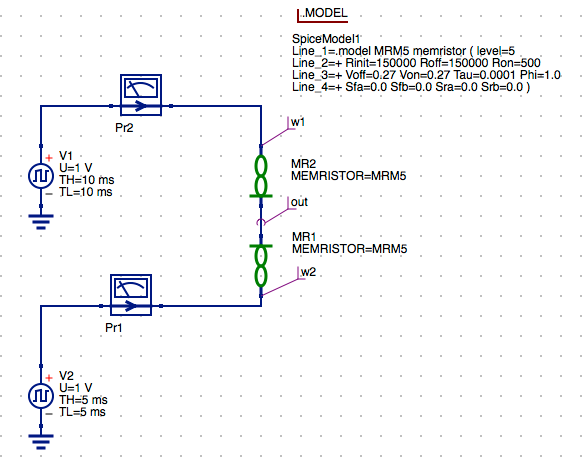

NOTE: We are using the AHaH 1-2 synapse AND configuration from the diagram above and the .Model directive MRM5, and the M-MSS model from the Knowm_Memristor_Technology library has been assigned for both the MR1 and MR2 memristor symbols. The Rinit parameter that models the memristor’s initial resistance was previous defined for the circuit by specifying a .PARAM statement. The Rinit has now been added to the .MODEL parameters list. In practice this model parameter should be set equal to the Roff parameter value for most circuits. We have increased the ratio for the Ron and Roff parameter values in the models as discussed in the Frey paper in order to the minimum and maximum values as measured at the output voltage across the divider network.

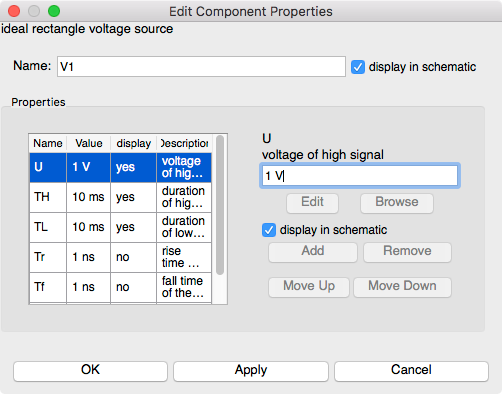

Pulse Voltage Source properties

- Double click

V1symbol on the schematic to open the parameters and review the settings for the Rectangle pulse source.

-

Select the

Urow in the properties table.The voltage is set to

1 Vso the output will be from0 Vto1 V. -

Select the

THrow in the properties table determine the time duration of the high pulses.We’ve set this value to

10 msto specify a10 mspulse width.Similarly the

TLrow in the properties table determine the time duration of the low pulses. I have set this also to10 msto specify a20 msperiod. -

Click

OKto exit the properties dialog. -

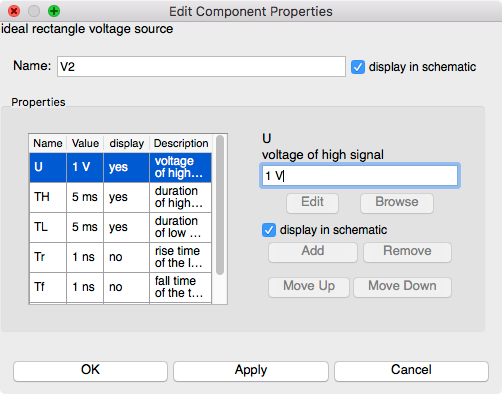

Similarly you can double click

V2symbol on the schematic to open the parameters and review the settings for second the Rectangle pulse source.

NOTE: The parameters for V2 are set to be half of the period of V1. This will give us twice the number of pulses on the input of the memristor MR2 and allow use to generate the truth table for the gate inputs.

Other Schematic Components

We have configured two current probes named Pr1 and Pr2 that are used to measure the current flowing through each memristor as the pulses are applied to the circuit. There are also the Name nodes w1 and w2 which will provide the voltage measured across the two memristors MR1 and MR2 respectively and represent the change of the weights and the memristor states based on the change in the conductance in each branch of the synapse.

The out named node provides the positive voltage for the voltage divider at the junction of the MR1 amd MR2 memristors which defines the logic state of the synapse which should should 0 V or 1 V at the maximum pulse values.

Transient Simulation Settings

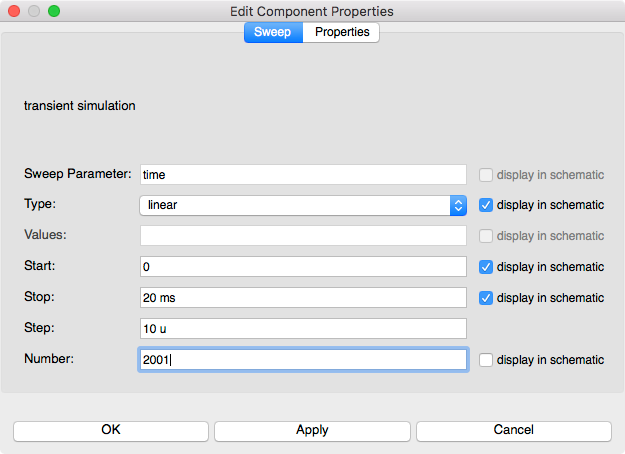

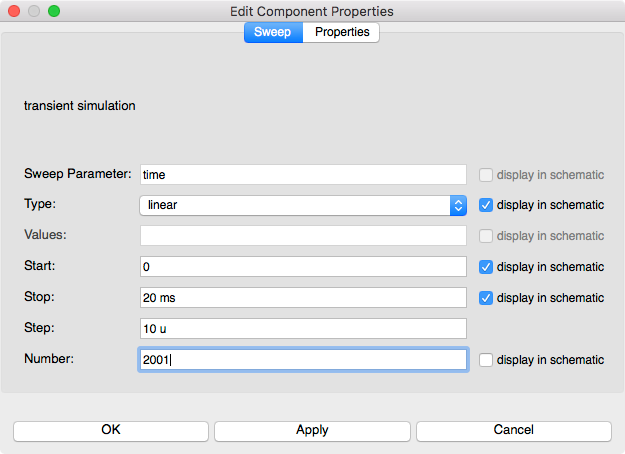

- Double click on the transient simulation symbol to open the setup parameters dialog.

I have entered

20 msin the stop field to coincide with the settings for the rectangle pulse sources totalperiod. I’ve entered2001in the number value field to set a10 usstep size. -

Click

Applyto save any changes. -

Click

OKto exit the properties dialog.

Save the Schematic Diagram File

The filename ahah_mr_AND2_2pl.sch has been used for this example schematic.

- Click the

Savebutton on the toolbar to save the schematic file.

Save Toolbar Button

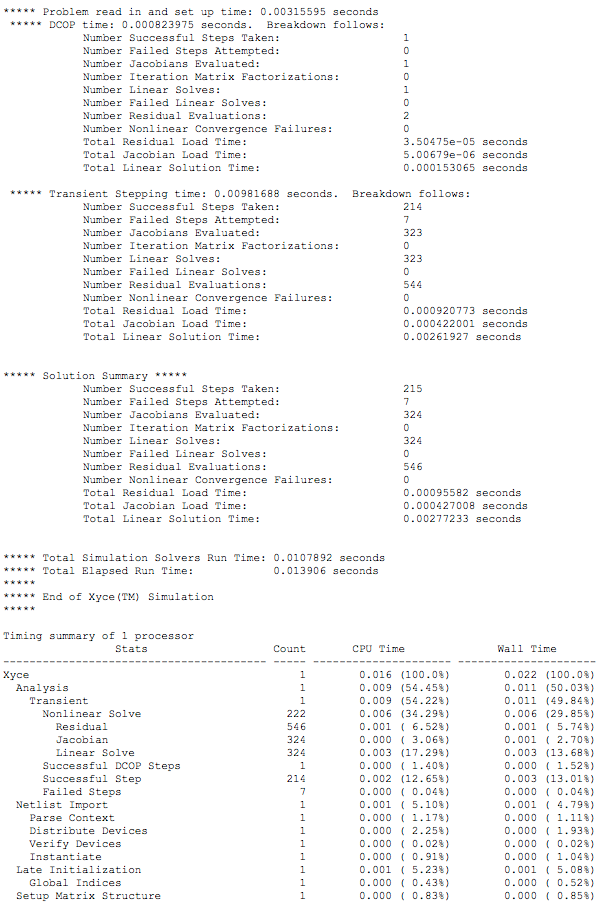

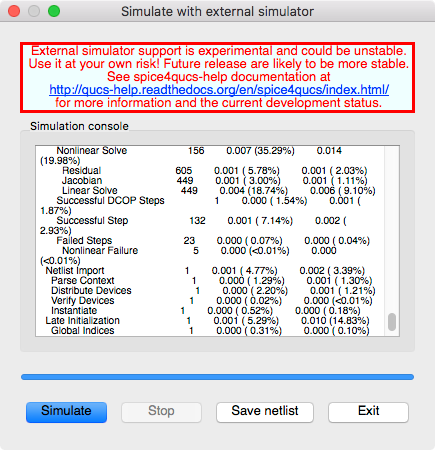

Run a Xyce Simulation

-

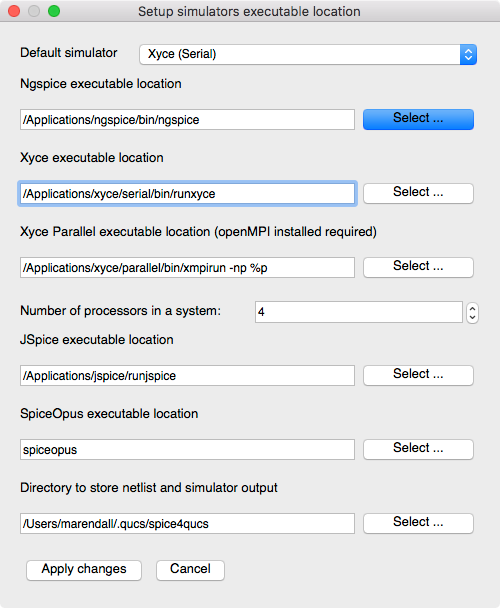

Verify the

Xyce executable locationis set to/Applications/xyce/serial/bin/runxyce -

Select

Simulation->Simulatefrom the main menu or selectSimulatebutton on the toolbar.

Run Simulation Toolbar Button

-

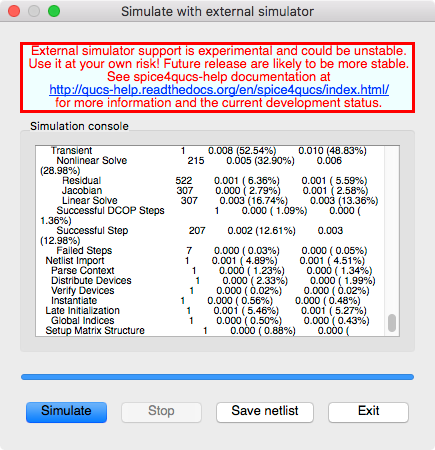

Check simulation for errors or warnings. See the status bar at the bottom of the Qucs window lower right corner.

-

You can save the current netlist by clicking the

Save Netlistbutton on the simulation window.NOTE: The

F6key orShow Last Netlistfrom the Simulations menu currently only displays the last netlist for the latest

Qucsator simulation. If you save the netlist using the button on the simulation window then you can open the.cirfile underOtherslist in the project tree.

-

Click the

Exitbutton to close theSimulationwindow. -

You can view and messages written by the Xyce simulator by clicking the

F5key or selectingShow Last Messagesfrom the Simulations menu.(…)

-

The

Qucsdata fileknowm_mr_AND2_2pl.dat.xyceproduced by the transient simulation will be automatically created in the$HOME/.qucs/AHaH_Logic_J_prj/directory.

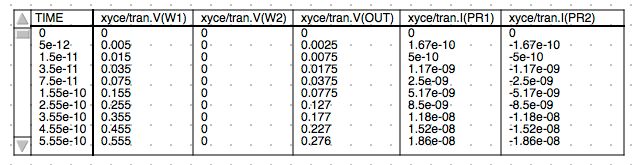

View the Tabular Results

-

Check the Tabular results.

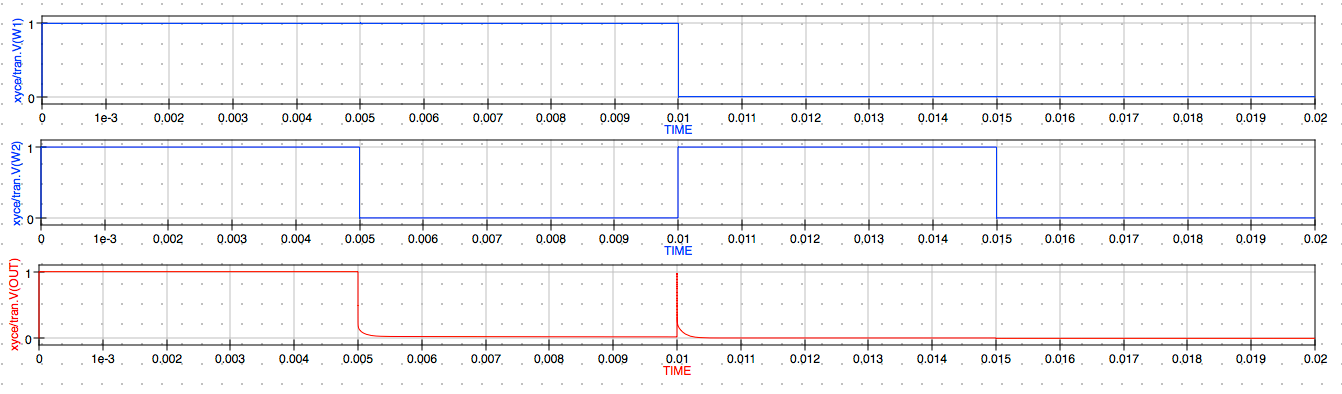

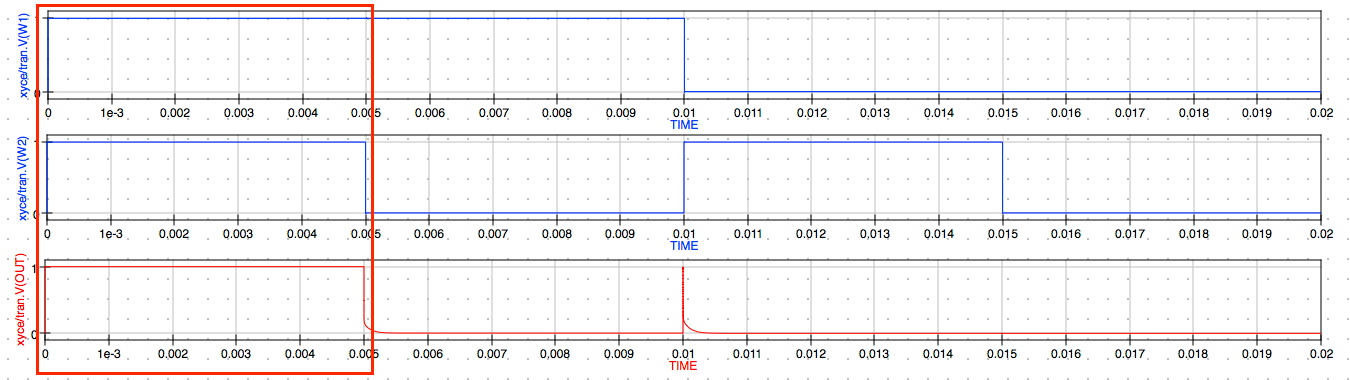

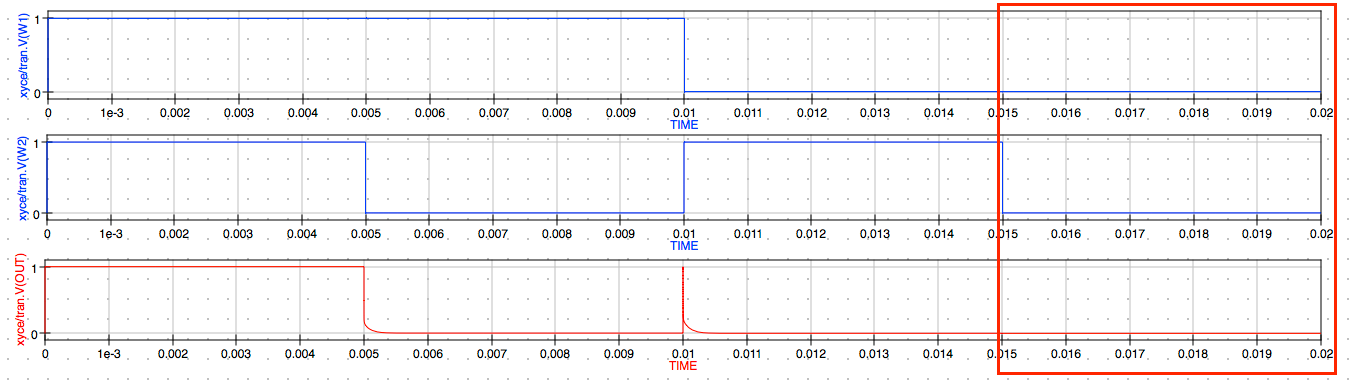

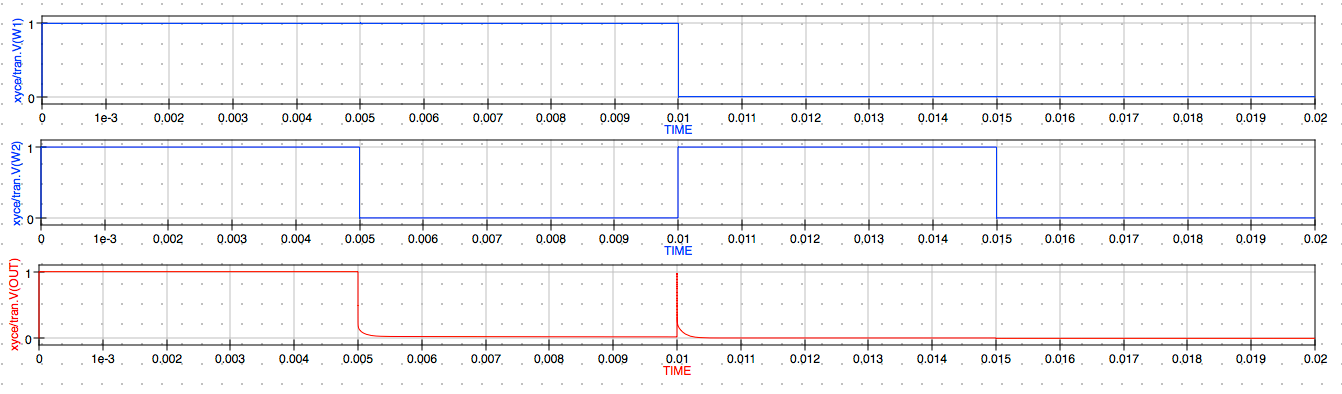

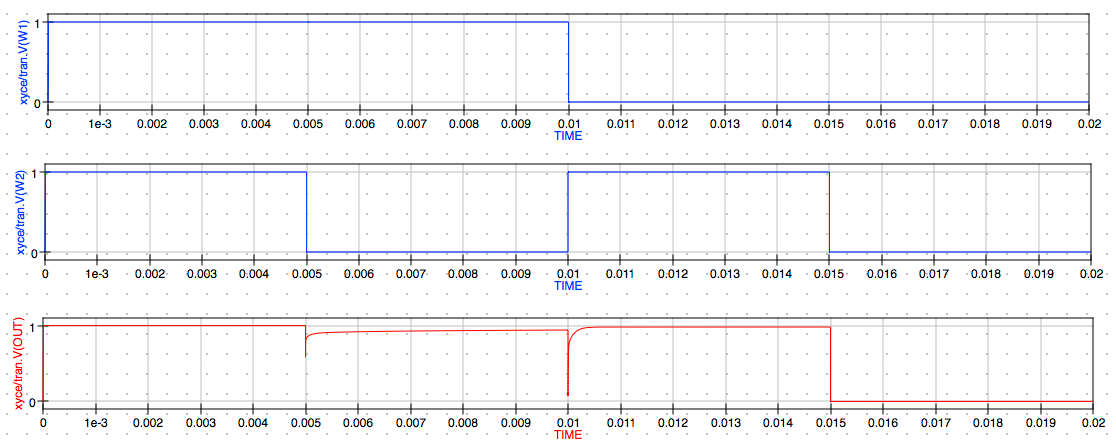

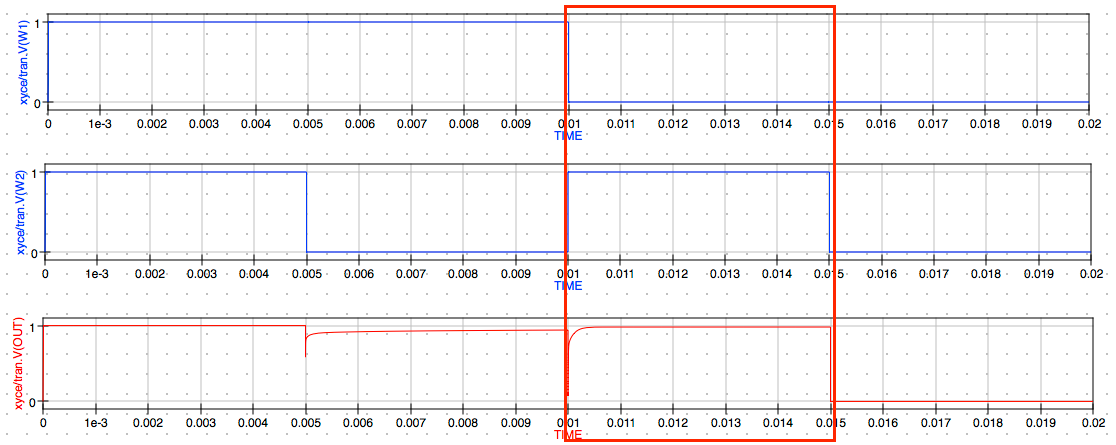

Cartesian Plot of Memristor-based AND2 Gate ( V vs. Time ) Results

-

You should also observe the results in the specified Cartesian plot defined in the schematic.

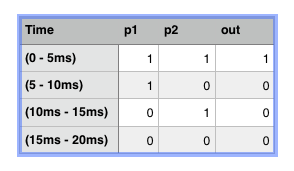

NOTE: The results contain multiple pulses of the 1 V amplitudes for w1 and w2 we defined in the Rectangle Pulse settings. This provides the 4 states of the AND gate for the following truth table.

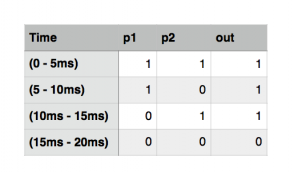

AND2 Circuit Truth Table

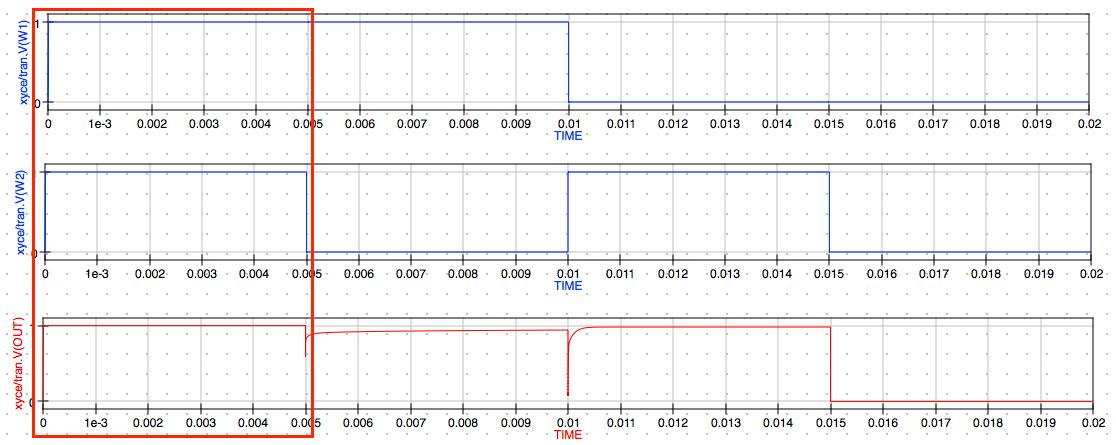

In the first 5 ms both V(w1) and V(w2) are positive 1 V so the V(out) state is also positive 1 V or logic 1.

First Logic State ( 0 – 5ms )

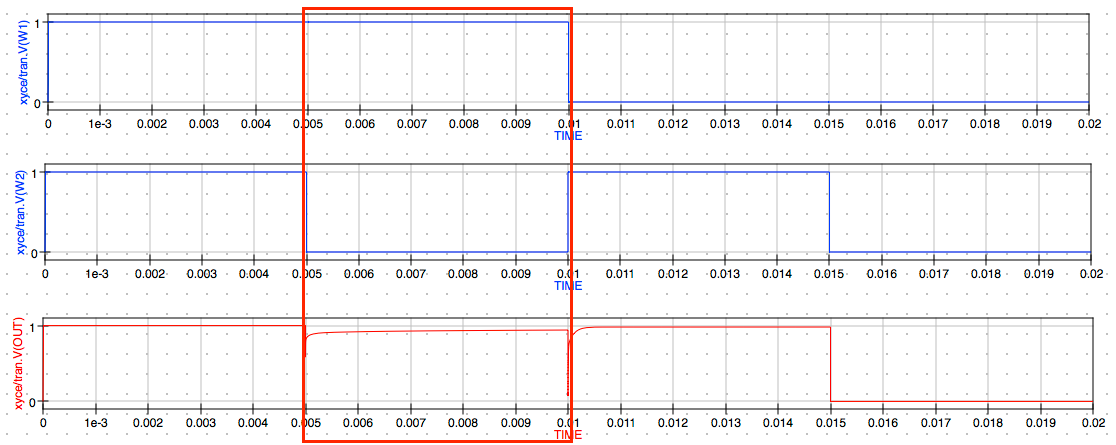

In the next 5 ms both V(w1) is positive 1 V but V(w2) is 0 V so the V(out) state is 0 V or logic 0.

Second Logic State ( 5ms – 10ms )

In the next 5 ms both V(w1) is 0 V but V(w2) is 1 V so the V(out) state is still 0 V or logic 0.

Third Logic State (10ms – 15ms)

In the last 5 ms both V(w1) and V(w2) are 0 V so the V(out) state is also 0 V or logic 0.

Fourth Logic State (15ms – 20ms)

Select JSpice as the Default Simulator

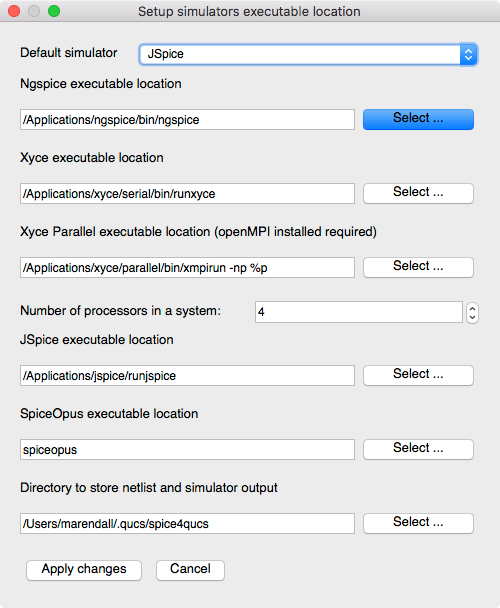

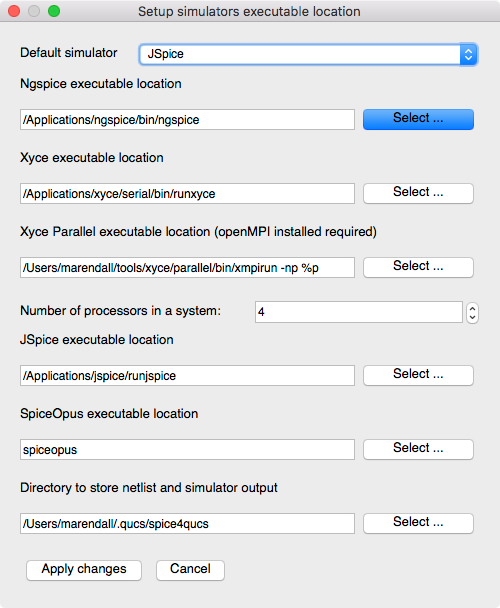

- Verify the

JSpice executable locationis set to/Applications/jspice/runjspice -

Select

Simulate->Select default simulator

-

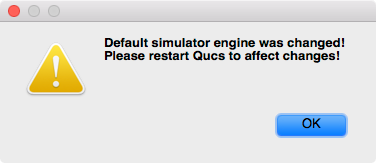

Select

JSpicefrom theDefault simulatordrop-down-list. -

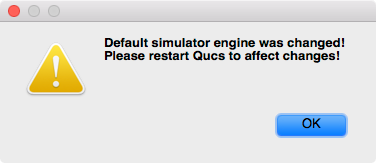

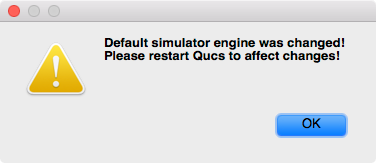

Click

Apply ChangesNOTE: After changing the default simulator you will receive a warning to restart Qucs. This is not always necessary unless you want to make the selected simulator the new default for the project. For now just proceed and we will discuss this in more detail below in the

General Notes on Usage.

-

Click

OK

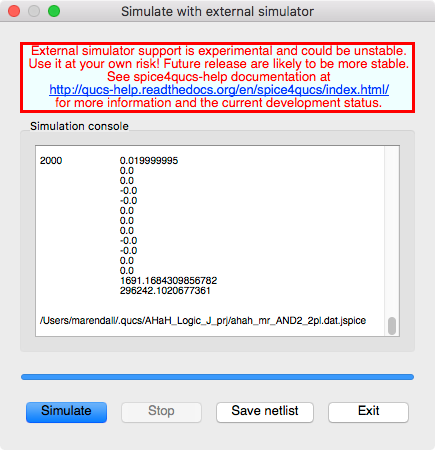

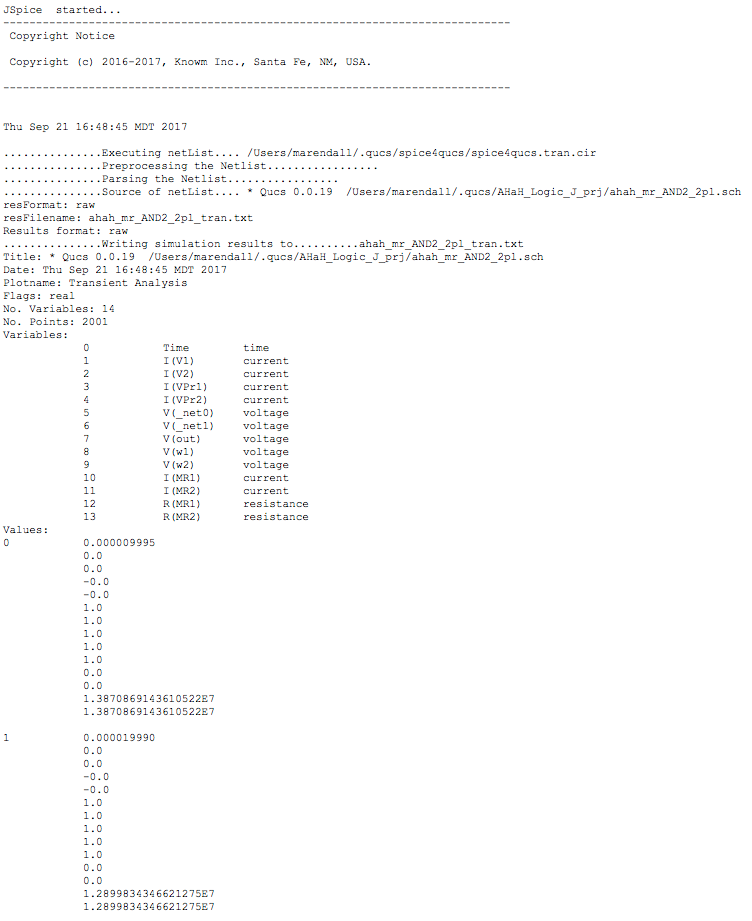

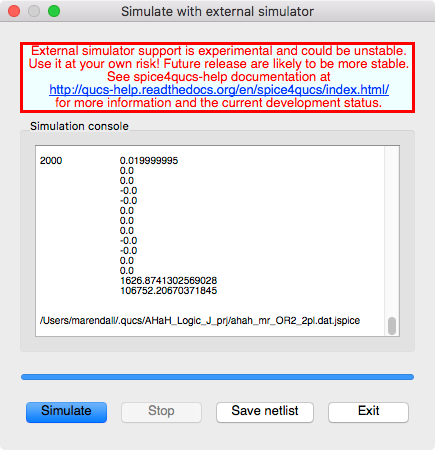

Run a JSpice Simulation

-

Select

Simulation->Simulateon the main menu or selectSimulatebutton on the toolbar.

Run Simulation Toolbar Button

-

Check simulation for

errorsorwarnings. See the status bar at the bottom of the Qucs windowlower right corner.

-

Again, if you want to save the current netlist, use the

Save netlistbutton on the external simulator window to open the file save dialog. Specify the name of the netlist to save, typically the schematic’s filename with the extension.cirinstead of.sch. The resulting file will be saved in the project folder and you can open the.cirfile under theOtherslist in the project tree.NOTE: The

F6key orShow Last Netlistfrom the Simulations menu currently only displays the last netlist for the latest Qucsator simulation.

-

Click the

Exitbutton to close theSimulationwindow. -

You can view any messages written by the simulator by clicking the

F5key or selectingShow Last Messagesfrom the Simulations menu.

(…)

-

The

Qucsdata fileknowm_mr_AND2_2pl.dat.jspiceproduced by the transient simulation will be automatically created in the$HOME/.qucs/AHaH_Logic_J_prj/directory.

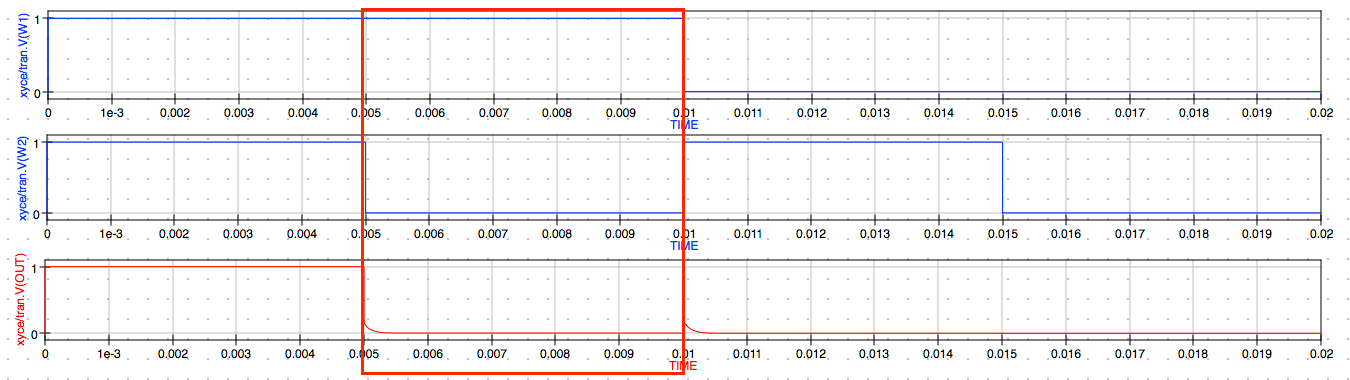

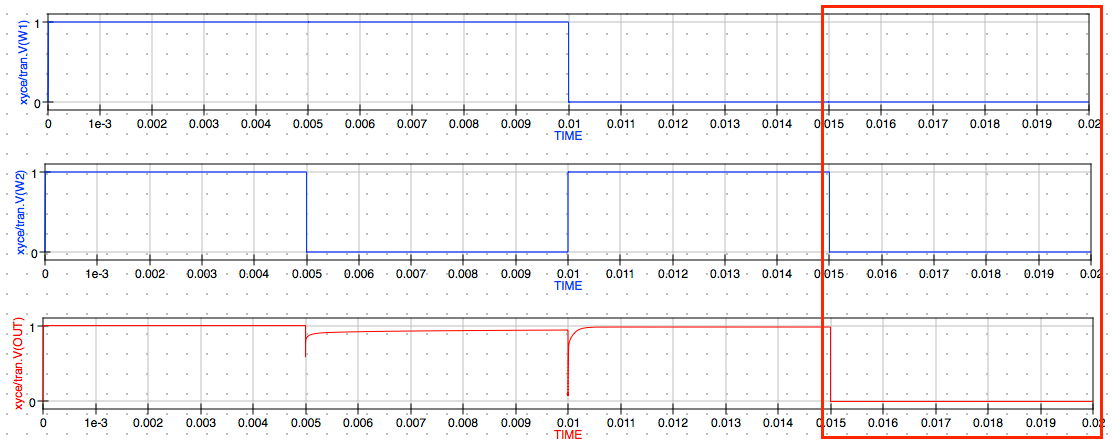

Cartesian Plot of Memristor V vs. Time Results

-

You should also observe the same results in the specified JSpice

V(w1),V(w2)andV(out)vs.Timeplot defined in the schematic.

NOTE: The results again contain

0 Vto1 VwithV(w1)having a pulse width of10 msat1 Vand10 msat0 Vwith a combined period of20 msand duty cycle of50%.V(w2)is set to output1 Vwith a pulse width of5 msandO Vwith pulse width of5 mswhich is also a combined10 msduty cycle50%but1/2the frequency ofV(w1). The simulated results closely agree with the Xyce simulation results above.

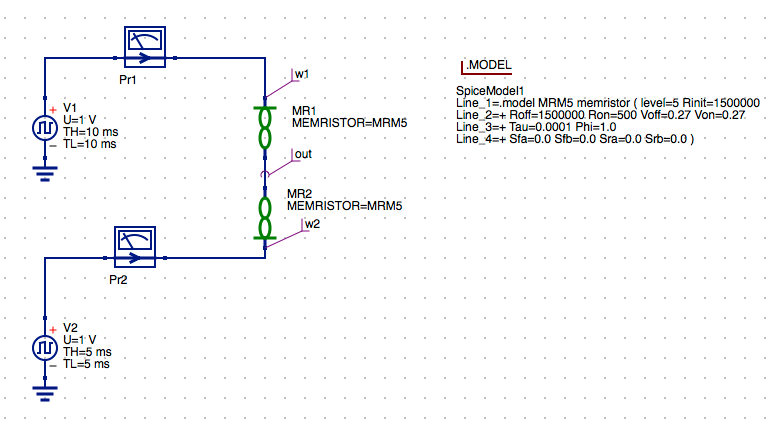

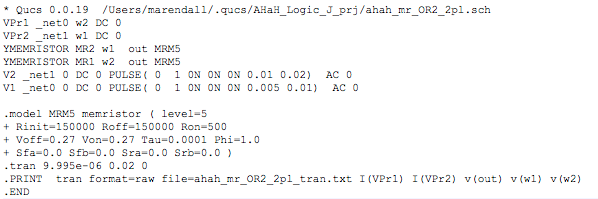

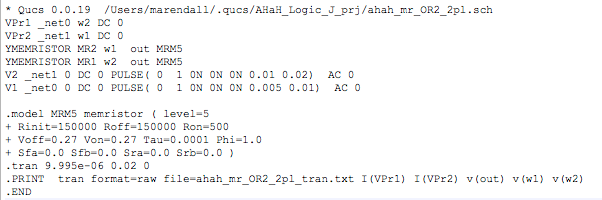

Open the ahah_mr_OR2_pl2 schematic diagram

-

Select the ahah_mr_OR2_pl2.sch from the Schematics list in the Contents tab of the Main Dock.

AHaH 1-2 OR2 Schematic

NOTE: Here we are using is the AHaH 1-2i synapse OR configuration from the diagram above and the .Model directive MRM5, the M-MSS model from the Knowm_Memristor_Technology library has been assigned for both the MR1 and MR2 memristor symbols.

AHaH 1-2i Logic OR Configuration

NOTE: Again the parameters for V2 are set to be half of the period of V1. This will give us twice the number of pulses on the input of the memristor MR2 and allow use to generate the truth table for the gate inputs.

Select Xyce as the Default Simulator

- Verify the

Xyce executable locationis set to/Applications/xyce/serial/bin/runxyce -

Select

Simulation->Select default simulator

-

Select

Xyce (Serial)from theDefault simulatordrop-down-list. -

Click

Apply ChangesNOTE: After changing the default simulator you will receive a warning to restart Qucs. This is not always necessary unless you want to make the selected simulator the new default for the project. For now just proceed and we will discuss this in more detail below in the

General Notes on Usage.

-

Click

OK

Configure the Transient Simulation

-

Double-click on the

transient simulationcomponent in the schematic.The

.TRANstart and end time have been set to0 sand20 msrespectively with2001points which will provide a step size of10 us.

-

Click

Applyto save the changes. -

Click

OKto exit the properties dialog.

Save the Schematic Diagram File

-

Click the

Savebutton on the toolbar to save changes to theahah_mr_OR2_pl2.schschematic file.

Save Toolbar Button

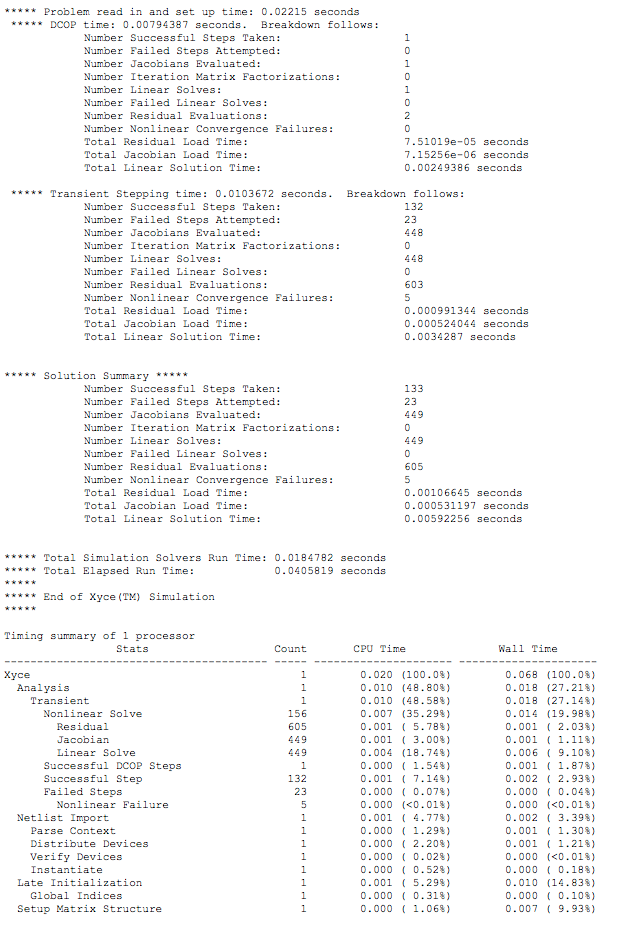

Run a Simulation

-

Press

Simulation->Simulateor selectSimulatebutton on the toolbar.

Run Simulation Toolbar Button

-

Check simulation for errors or warnings. See the status bar at the bottom of the Qucs window lower right corner.

-

Again, you can save the current netlist by clicking the

Save Netlistbutton on the simulation window.NOTE: The

F6key orShow Last Netlistfrom the Simulations menu currently only displays the last netlist for the latest

Qucsator simulation. If you save the netlist using the button on the simulation window then you can open the.cirfile underOtherslist in the project tree.

-

Click the

Exitbutton to close the Simulation window. -

You can view and messages written by the Xyce simulator by clicking the

F5key or selectingShow Last Messagesfrom the Simulations menu.(…)

-

The

Qucsdata fileknowm_mr_OR2_2pl.dat.xyceproduced by the transient simulation will be automatically created in the$HOME/.qucs/AHaH_Logic_J_prj/directory.

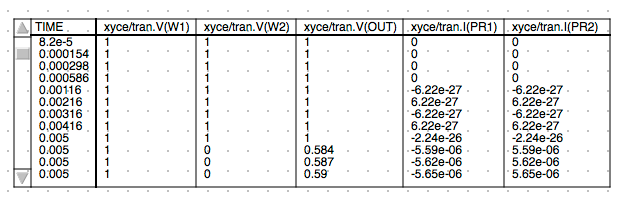

View the Tabular Results

-

Check the Tabular results.

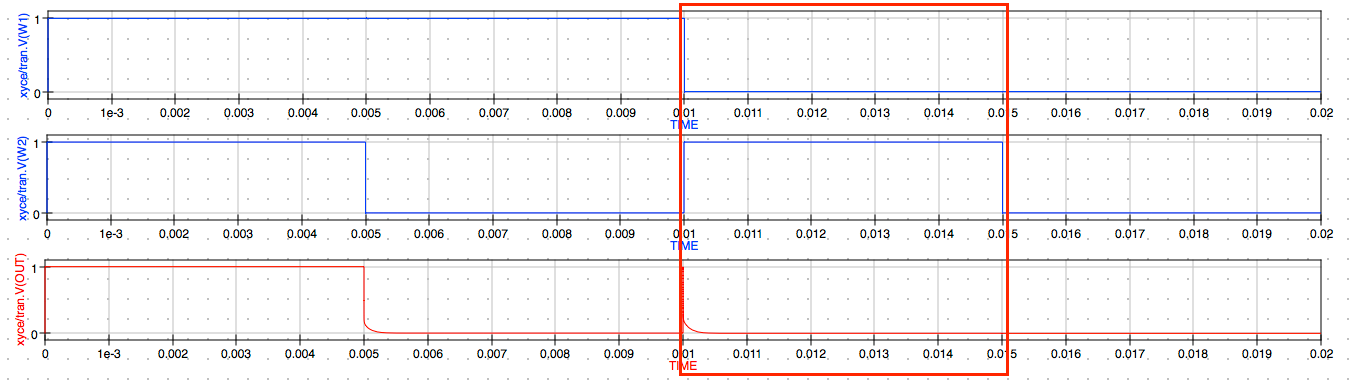

Cartesian Plot of Memristor-based OR2 Gate ( V vs. Time ) Results

-

You should also observe the results in the specified Cartesian plot defined in the schematic.

Voltage Input, Output with Memristor Power vs. Time

NOTE: The results contain multiple pulses of the 1 V amplitudes for w1 and w2 we defined in the V1 and V2 pulse settings. This plot provides the 4 states of the AND gate as shown before by the plot of V(out).

OR2 Circuit Truth Table

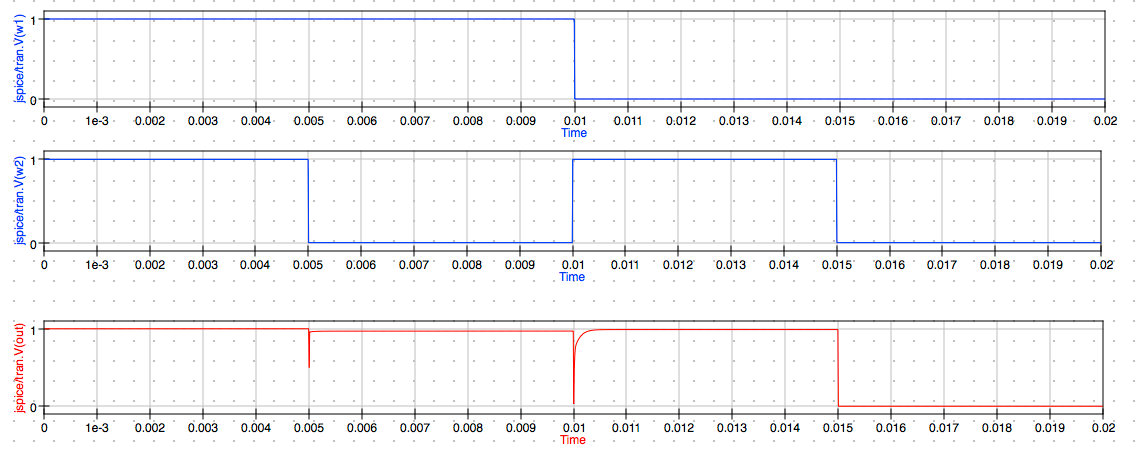

In the first 5 ms both V(w1) and V(w2) are positive 1 V so the V(out) state is also positive 1 V or logic 1.

First Logic State ( 0 – 5ms )

In the next 5 ms both V(w1) is positive 1 V but V(w2) is 0 V so the V(out) state is 1 V or logic 1.

Second Logic State ( 5ms – 10ms )

In the next 5 ms both V(w1) is 0 V but V(w2) is 1 V so the V(out) state is still 1 V or logic 1.

Third Logic State (10ms – 15ms)

In the last 5 ms both V(w1) and V(w2) are 0 V so the V(out) state is also 0 V or logic 0.

Fourth Logic State (15ms – 20ms)

Select JSpice as the Default Simulator

- Verify the

JSpice executable locationis set to/Applications/jspice/runjspice -

Select

Simulation->Select default simulator

-

Select

JSpicefrom theDefault simulatordrop-down-list. -

Click

Apply ChangesNOTE: After changing the default simulator you will receive a warning to restart Qucs. This is not always necessary unless you want to make the selected simulator the new default for the project. For now just proceed and we will discuss this in more detail below in the

General Notes on Usage.

-

Click

OK

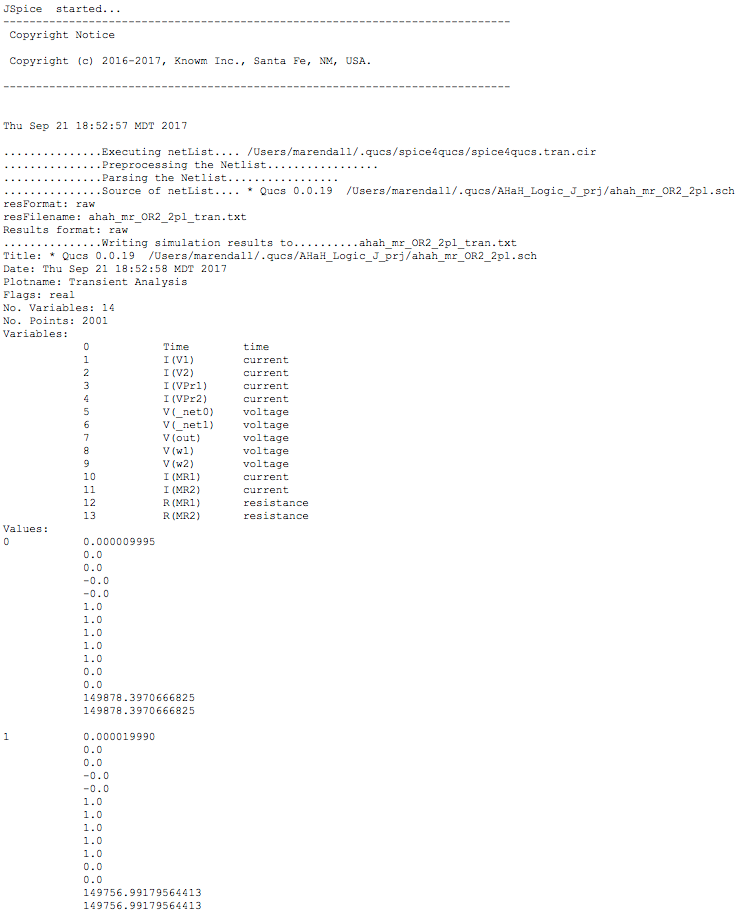

Run a JSpice Simulation

-

Select

Simulation->Simulateon the main menu or selectSimulatebutton on the toolbar.

Run Simulation Toolbar Button

-

Check simulation for

errorsorwarnings. See the status bar at the bottom of the Qucs windowlower right corner.

-

Again, if you want to save the current netlist, use the

Save netlistbutton on the external simulator window to open the file save dialog. Specify the name of the netlist to save, typically the schematic’s filename with the extension.cirinstead of.sch. The resulting file will be saved in the project folder and you can open the.cirfile under theOtherslist in the project tree.NOTE: The

F6key orShow Last Netlistfrom the Simulations menu currently only displays the last netlist for the latest Qucsator simulation.

-

Click the

Exitbutton to close theSimulationwindow. -

You can view any messages written by the simulator by clicking the

F5key or selectingShow Last Messagesfrom the Simulations menu.

(…)

-

The

Qucsdata fileknowm_mr_OR2_2pl.dat.jspiceproduced by the transient simulation will be automatically created in the$HOME/.qucs/AHaH_Logic_J_prj/directory.

Cartesian Plot of Memristor V vs. Time Results

-

You should observe similar results in the specified JSpice

V(w1),V(w2)andV(out)vs.Timeplot defined in the schematic.

NOTE: The results again contain 0 V to 1 V with V(w1) having a pulse width of 10 ms at 1 V and 10 ms at 0 V with a combined period of 20 ms and duty cycle of 50%. V(w2) is set to output 1 V with a pulse width of 5 ms and O V with pulse width of 5 ms which is also a combined 10 ms duty cycle 50% but 1/2 the frequency of V(w1). The simulated results closely agree with the Xyce simulation results above.

That completes this tutorial. Try designing your own schematic files and add them to the AHaH_Logic_J_prj project. Additional experiments can be developed using the features presented here. In future tutorials we will explore more circuits using AHaH nodes to simulate machine learning algorithms implemented in hardware.

JSpice is still under development and we will be adding features that are most useful to our mission to provide OSS EDA tools to those of you who are interested in developing neuromorphic circuits using memristor-based synapses. We will be accepting feedback and will be building a wish list for additional requested features for JSpice that may be found in other SPICE compatible simulators. Please leave a comment or send us e-mail through the knowm.org site’s contact page.

You should also checkout the documentation and other examples listed in the Qucs 0.0.19 and Qucs-S 0.0.19 documentation available on the web at the following URLs.

References

- Comparing Simulation Results of the Knowm M-MSS Model in Xyce and JSpice Using Qucs-S

- Simulating Knowm AHaH Memristor-Based Logic Using Qucs-S and Xyce

- JSpice GitHub repository

- Qucs 0.0.19 Help: https://qucs-help.readthedocs.io/en/0.0.19/subcircuit.html

- Qucs-S 0.0.19 Help: https://qucs-help.readthedocs.io/en/spice4qucs/SPICEComp.html

- Qucs-S Bugtracker: https://github.com/ra3xdh/qucs/issues

- Qucs-S Sub-project Home Webpage: https://ra3xdh.github.io/

General Notes on Usage

Default simulator selection

When selecting a new default simulator, if you want the change to be persistent after closing Qucs-S then you need to do the following steps.

- Select

Simulation->Select default simulator -

Select the simulator in the

Default simulatordrop-down list. -

Click

Apply changes -

Select

File->Application Settings -

Click

Applyto save the settings. -

Click

OKto exit the dialog. -

Select

Qucs->Quit QucsNOTE: Several of the features of the Qucs-S user interface are displayed based on the

Default simulatorwhich is saved in theQucsSettingsfile updated when you save theApplication Settingsfor the program. If you don’t perform the steps outlined above before closing Qucs-S then theDefault simulatorselection will not be saved and the will not be set when reopening Qucs-S. This issue should be corrected in a future version of the software.

Other References

- What is Qucs?

- What can all be installed from Sourceforge?

- Qucs Website: http://qucs.sourceforge.net/

- Main Repository: https://sourceforge,net/p/qucs/git/ci/master/tree/

- Mirror Repository: https://github.com/Qucs/qucs

- Mailing lists: http://sourceforge.net/p/qucs/mailman/

- Forum: http://sourceforge.net/p/qucs/discussion/

- Bug trackers:

- Source code documentation:

- Wiki: https://github.com/Qucs/qucs/wiki

Leave a Comment